- 咨询热线:13823554249

- 【安康】切换分站

一、背景

随着电子器件朝着小型化、便携化方向发展,电子器件的组装也越来越集约化。挠性线路板,由于其具有体积小、重量轻、线路密度高等优点,逐渐地取代了传统导线在电子器件组装的作用。从近几年来,挠性线路板(FPC)占印制线路板(PCB)市场份额从不足10 %提高至20 %以上,也证明了FPC市场需求的发展。

FPC作为电子器件中的连接线,主要是起到导通电流和传输信号的作用。当信号传输线分布在FPC最外层时,为了避免信号传输过程受到电磁干扰而引起信号失真,FPC在压合覆盖膜后会再压合一层导电层(电磁屏蔽膜),起到屏蔽外面电磁干扰的作用。其中最常见的是数码相机中作为图像信号传输的FPC。作为传输线的FPC通常有着特殊的阻抗要求,但压合电磁屏蔽膜后的FPC结构出现变化,其阻抗计算方式也需要进行修正。因此,本文通过FPC压合电磁屏蔽膜后的阻抗变化研究,修正其阻抗计算方式,为FPC压合电磁屏蔽工程设计时提供参考。

二、试验设计

1.试验材料

PI基无胶板材:PI厚 2 mil,铜厚0.5/0.5 OZ;

覆盖膜:PI厚 0.5~2 mil,胶厚25~35 μm;

电磁屏蔽膜:导电胶厚 10 um,PI厚 6-10 μm。

试验、测试设备及条件

快压机、网络分析仪。

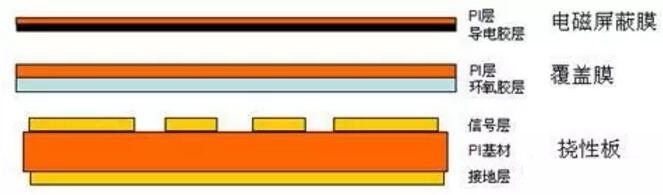

2.试板叠层

在挠性板上依次压合覆盖膜、电磁屏蔽膜

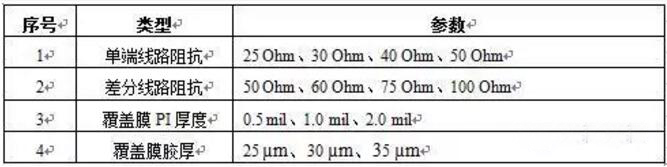

3.试验参数

3.结果与讨论

挠性板阻抗的变化

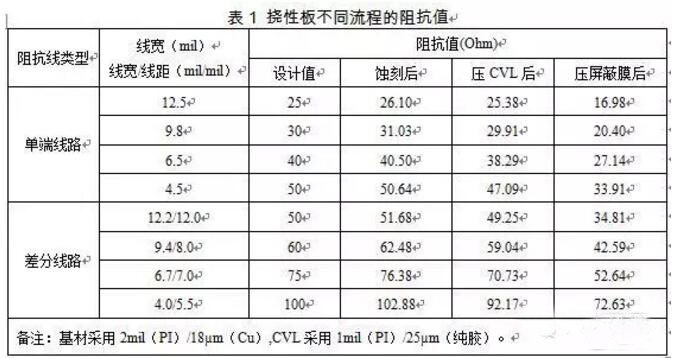

压合电磁屏蔽膜的挠性板一般为双面板,顶层分布信号传输线路,底层为接地层。实验采用了双面挠性板结构,以蚀刻后的线路阻抗为基准,分别设计了单端线路25~50 Ohm和差分线路50~100 Ohm,依次在线路蚀刻后、压合CVL后、压屏蔽膜后测试线路的阻抗值,结果如表1所示。

从表1可以看出,在线路蚀刻后,实测阻抗线的阻抗值与设计值仅有0.5~3.0 Ohm的偏差。从偏差的百分比来看,所有阻抗线的阻抗值与设计值的偏差于小于5 %。对于双面挠性板而言,其基材与面铜的厚度相对稳定。因此,可以说通过蚀刻过程对线宽的控制以达到对线路阻抗的精确控制。

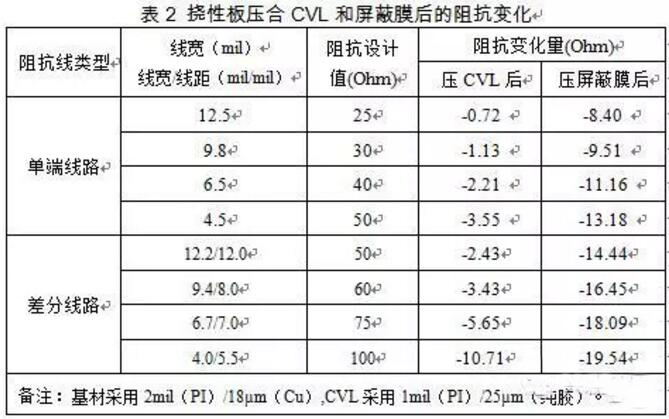

从不同流程后的线路阻抗对比上可以看出,在蚀刻后的线路上依次压合CVL、电磁屏蔽膜后其阻抗值均呈现下降,如表2所示。

从表2可以看出,对比双面挠性板分别在压合CVL后和压合电磁屏蔽膜后的阻抗变化量,压合CVL后的阻抗减少量远小于压合电磁屏蔽膜后的阻抗减少量。可见,压合电磁屏蔽膜后的阻抗计算模式不同于压合CVL的。因此,需要对压合电磁屏蔽膜后的挠性板阻抗计算方式进行确认。

4.不同阻抗计算模型对比

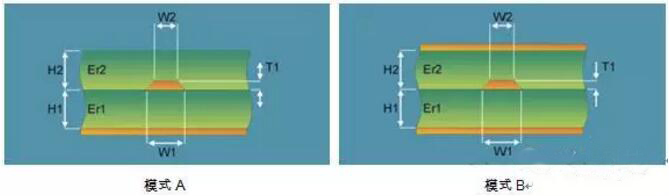

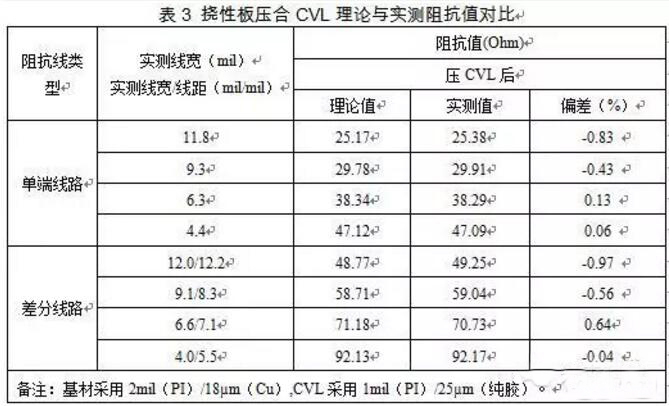

目前,挠性板压合CVL的阻抗计算主要是采用图1中模式A进行计算,将CVL当作线路上的介质层。结合以往的研究经验,采用纯胶层介电常数为2.0,PI层介电常数为2.7,通过实际测量的线宽/线距,可计算出双面挠性板压合CVL后的理论阻抗,并与实际测试的阻抗作对比,结果如表3所示。

从表3可以看出,压合CVL后的挠性板理论阻抗值与实际测量值非常接近,两者的偏差均在1%以内。由此可见,采用图1中的模式A可以很好地模拟挠性板压合CVL的理论阻抗。

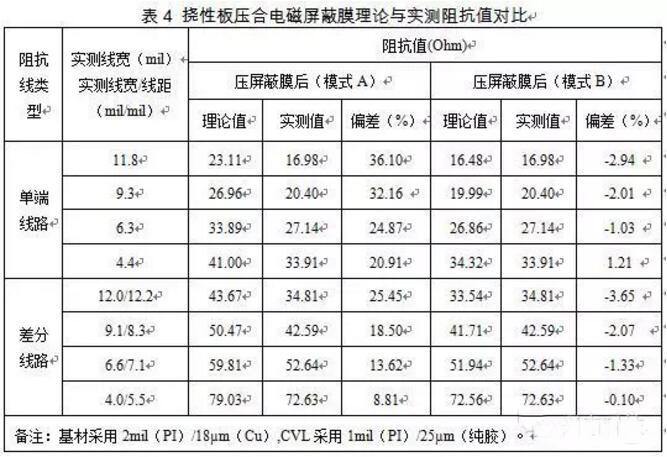

对于挠性板压合电磁屏蔽膜后的理论阻抗计算,目前存在着两种方式:一是将电磁屏蔽膜当成一层介质层,即采用图1中模式A进行计算,这种模式将双面挠性板的线路视为外层微带线的结构;二是将电磁屏蔽膜的导电层当作成一层铜皮,即采用图1中模式B进行计算,这种模式将双面挠性板的线路视为内层带状线的结构。将供应商所提供的电磁屏蔽膜介电常数68.3、纯胶层介电常数为2.0和PI层介电常数为2.7,分别采用图1中的模式A和模式B并根据实测的线宽线距进行理论阻抗计算,结果如表4所示。

从表4可以看出,采用外层微带线的模式A结构进行压合电磁屏蔽膜的双面挠性板理论阻抗计算时,理论阻抗与实测阻抗存在着8.81~36.10 %的偏差。而采用内层带状线的模式B结构进行压合电磁屏蔽膜的双面挠性板理论阻抗计算成本时,理论阻抗与实测阻抗之间的偏差均在4 %以内。比起模式A,采用模式B计算双面挠性板压合电磁屏蔽后的理论阻抗更加准确。由此可见,双面挠性板压合电磁屏蔽后的理论阻抗应当采用内层带状线的结构,将电磁屏蔽膜视为一层铜箔。

5.覆盖膜PI/胶厚对阻抗的影响

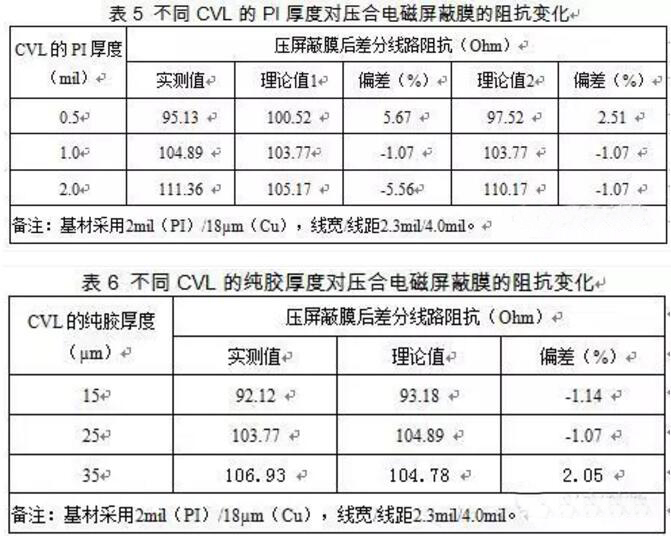

当双面挠性板压合电磁屏蔽膜采用内层带状线的结构进行理论阻抗计算,覆盖膜则成了双面挠性板线路上的介质层。而从以往的研究经验可知,为了使得双面挠性板的理论阻抗更值接近实际测量阻抗值,我们将覆盖膜的PI与纯胶分别作为不同的介质进行区分。因此,覆盖膜PI厚度或纯胶厚度的变化也会影响到挠性板的阻抗变化。实验分别对比了在CVL中0.5~2.0mil的PI厚度和15~35μm的纯胶厚度,结果如表5-6所示。

从表5可以看出,阻抗理论值1是统一采用PI介电常数为2.7进行计算的,0.5 mil和2 mil厚PI的理论值与阻抗实测值的偏差均超过了5%。而根据PI的厚度对PI的介电常数进行调整,分别调整为0.5 mil厚PI的介电常数为2.5、2.0 mil厚PI的介电常数为3.1,所计算出的阻抗理论值2与实测值偏差均小3 %。因此,需要针对不同CVL的PI厚度对其介电常数进行调整。

而从表6中CVL的不同纯胶厚度对比可以看出,纯胶按介电常数2.0进行计算所得的阻抗理论值与实测值偏差均小于2.5 %。也即是说,CVL的纯胶可以按统一的介电常数进行计算。

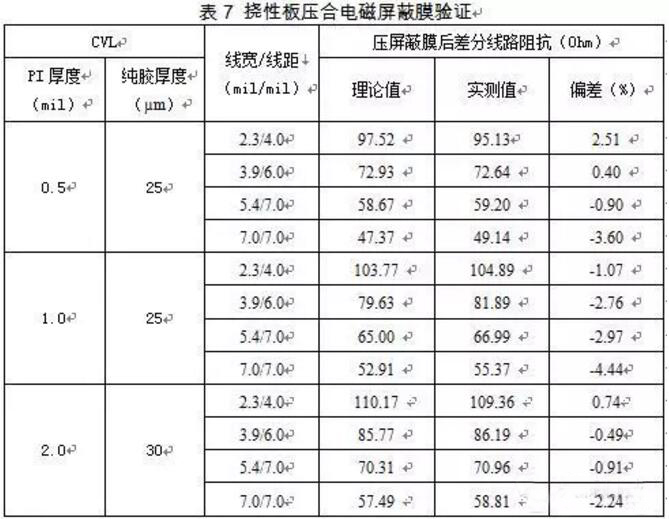

为了验证以上分析过程中正确性,实验采用了不同CVL的PI厚度和纯胶厚度,分别测试的实际阻抗值与理论阻抗值,结果如表7所示。从表7中可以看出压合电磁屏蔽膜的挠性板其阻抗实测值与理论值偏差均小于5 %,即通过以上的分析可以正确地预估压合电磁屏蔽膜挠性板的理论阻抗值。

三、结论

通过以上的分析可以得到以下几点结论:

对于挠性板压合电磁屏蔽膜来说,阻抗值计算可采用内层带状线结构的计算方式进行;

CVL的PI介电常数需要根据厚度进行调整。